分類:ハーネスアセンブリ

一、阻抗不匹配の主要な結果

抵抗不連続は高速信号に多様な影響を及ぼします。まず、信号の反射と眼図の閉じが波形の歪みを引き起こし、特にMIPI D-PHY、LVDS、USB 3.x、DisplayPortなどの高速インターフェースがこの影響を受けやすいです。次に、抵抗不適合がEMI/EMCの問題を悪化させ、多芯線束の共模干渉と交叉干渉が拡大され、システムの電磁適合性に影響を与えます。最後に、それは伝送遅延と大きさの減衰を引き起こし、信号到達時間の不一致(skew)が発生し、画面の点滅や画像のフレームの誤差が引き起こされる可能性があります。特に高速撮影や表示アプリケーションにおいて顕著です。

二、阻抗不匹配の常见原因

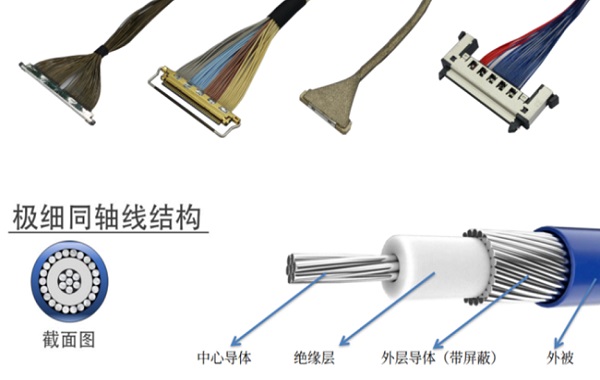

抵抗不協和は通常設計と組み立て段階で発生します。まず、同軸構造の設計不良、例えば導体直径、介质厚みまたは屏蔽密度の偏差が特性抵抗を直接変えることがあります。次に、加工組み立ての誤差、例えば圧着、溶接または剥皮が過剰である場合も幾何学的な一致性を損なうことがあります。さらに、コネクタの選定不適合も原因です。一部のマイクロコネクタ(例えばHirose、I-PEX シリーズ)は抵抗容差に対する要求が高くなります。最後に、PCB端の抵抗一致ネットワークの設計欠陥、例えば端子抵抗が不精確または走線の過渡が不良である場合も全体の抵抗不連続を引き起こすことがあります。

三、阻抗匹配の効果的な戦略

阻抗不適合の解決には、デザインからテストまでの全プロセスを最適化する必要があります。まず、ケーブル構造の一致性を保ち、導体、媒体、シールドのサイズを厳しく制御し、サンプル段階でTDRテストを通じて阻抗の連続性を確認します。次に、マッチングの高精度なコネクタを選択し、端接長さと圧着深度を最適化し、必要に応じてステップ溶接構造を用います。さらに、PCB端で走線幅、媒体厚み、差分間隔を制御し、ケーブルの阻抗と一致させることで、端末にマッチング抵抗を追加します。最後に、多重シールド、360°接地、テストによるフィードバックループを通じて、共模干渉を低減し、信号の完全性を確保します。